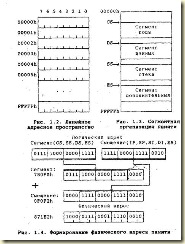

Память процессора логически организована в виде линейного адресного пространства как одномерный массив байт (рис. 1.2.), каждый из которых имеет 20 – битовый физический адрес в диапазоне 00000h – FFFFFh (здесь и далее представляются в шестнадцатеричной системе счисления, признаком которой служит буква h в конце числа). Любые две смежных байта в памяти могут рассматриваться как 16 – битовое число. Младший байт имеет меньший адрес, старший – больший. Адресом слова считается адрес его младшего байта (располагается по меньшему адресу). Таким образом, любой физический адрес является одновременно адресом байта и адресом слова. Нумерация бит в каждом байте (слове) выполняется начиная с младшего разряда от 0 до 7 (от 0 до 15). Каждый байт (слово) может содержать число от 0 до 255 (от 0 до 65535) в беззнаковом представлении и от –128 до +127 (от –32768 до +32767) – при представлении в дополнительном коде.

Физический адрес формируется процессором для обращения к внешней памяти. Физическое пространство памяти в 1мБайт представляется как набор сегментов. Сегмент состоит из смежных ячеек памяти и является независимой и отдельно адресуемой единицей памяти емкостью 64 КБайта (рис. l.3). Начальные адреса четырех сегментов, выбранных в качестве текущих, записываются в сегментные регистры процесcopa CS, DS, SS и ES, тем самым фиксируются текущие сегменты кода (программы), данных (операндов), стека и дополнительных данных. Для обращения к командам и данным, находящимся в других сегментах, необходимо изменять содержимое сегментных регистров, что позволяет использовать все пространство памяти.

В сегментном регистре хранятся 16 старших разрядов 20-битового начального адреса сегмента. Четыре младших разряда принимаются равными нулю и дописываются слева к содержимому сегментного регистра при вычислении физических адресов ячеек памяти. Поэтому начальные адреса ячеек всегда кратны 16. Поскольку других ограничений на размещение сегментов в памяти нет, сегменты могут быть соседними (смежными), частично или полностью перекрывающимися. Физическая ячейка памяти может принадлежать одному или нескольким сегментам одновременно.

Логический адрес ячейки памяти используется для представления адресов в программах и состоит из двух 16-битовых беззнаковых величин: начального адреса сегмента (содержимое используемого сегментного регистра) и внутрисегментного смещения, которое задает расстояние от начала сегмента до адресуемой ячейки памяти! Для вычисления физического адреса по заданному логическому содержимое сегментного регистра (сегментный адрес) умножается на 16 (сдвигается влево на 4 бита) и суммируется с внутрисегментным смещением, как показано на рис. 1.4, где также приведены возможные источники компонентов логического адреса (ЕА — эффективный адрес, вычисляемый в соответствии с заданным способом адресации, который определяется текущей исполняемой командой).

При суммировании сегментного адреса и смещения для получения физического адреса может возникнуть перенос за пределы разрядной сетки, который игнорируется. Это приводит к кольцевой организации памяти, при которой за ячейкой с максимальным адресом FFFFFh следует ячейка с нулевым адресом OOOOOh.

Процессор при своем функционировании выполняет обращения к внешней памяти, подключаемой к шине процессора. Источники логического адреса для различных обращений процессора к памяти не совпадают. Команды процессор всегда считывает из текущего сегмента кода в соответствии с содержимым пары регистров CS:IP. Регистр CS содержит адрес сегмента, регистр IP — смещение текущей исполняемой команды в этом сегменте. После выборки каждой команды содержимое регистра IP увеличивается на длину команды.

Стековые команды всегда обращаются к текущему сегменту стека по адресу в паре регистров SS:SP. Регистр SS хранит базовый адрес сегмента стека, а регистр SP указывает на вершину стека, т.е. содержит смещение вершины стека в текущем стековом сегменте. При обращении к стеку пересылается одно слово; при занесении слова в стек оно помещается на вершину стека и указатель SP уменьшается на 2; при извлечении из стека считывается слово с вершины стека и указатель стека увеличивается на 2. Таким образом стек растет в сторону меньших адресов.

Операнды команд, выполняемые процессором, размещаются в текущем сегменте данных, и обращение к ним осуществляется по адресу DS:EA, где ЕА эффективный адрес (смещение ячейки данных в текущем сегменте данных) и определяется специальным полем в коде команды. Некоторые команды процессора могут использовать данные, расположенные в дополнительном сегменте. В этом случае обращение осуществляется по адресу ES:EA.